Подвійні стандарти

Минуло трохи більше двох місяців, як ми анонсували Raspberry Pi 5, і час пролетів непомітно. Ми знали, що створили щось особливе, але були приголомшені позитивною реакцією спільноти.

Швидкість виробництва була більшою, ніж для будь-якого попереднього флагманського продукту: протягом останніх кількох тижнів ми виробляли 70 000 одиниць на тиждень, і планується, що до кінця січня ця швидкість зросте до 90 000 одиниць на тиждень.

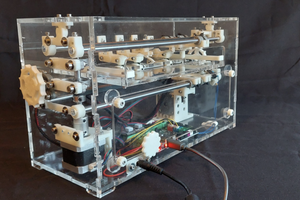

Коли люди оговталися від шоку, побачивши кнопку живлення та годинник реального часу на Raspberry Pi, однією з найбільш коментованих особливостей нової платформи став маленький вертикальний 16-канальний FFC (плоский гнучкий кабель). ) роз’єм на лівій стороні плати, який відкриває одноканальний інтерфейс PCI Express.

16-канальний FFC (плоский гнучкий кабель)

PIP PIP

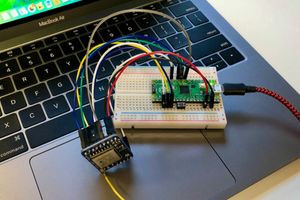

Peripheral Component Interconnect Express (PCI Express або PCIe), як випливає з назви, це з’єднання на рівні плати, яке забезпечує високошвидкісну передачу даних між чіпом процесора (у нашому випадку BCM2712) і зовнішніми периферійними пристроями, такими як NVMe SSD, карти Ethernet, або більш екзотичні речі, такі як прискорювачі AI/ML.

PCIe працює шляхом серіалізації передачі даних і надсилання по одному біту в один канал. Кожен канал надсилає дані на одну або кілька «диференціальних пар» на друкованій платі, які в основному є керованими хвилеводами, створеними двома близько розташованими проводами (з заземленою поверхнею внизу), які можуть передавати дуже швидкі сигнали з високою стійкістю до перешкод і низькими втратами та спотвореннями сигналу. Для односмугового (×1) інтерфейсу PCIe ми маємо одну пару передачі, одну пару прийому та пару тактових сигналів. Це означає, що потрібні три диференціальні пари (і шість проводів). Інтерфейси PCIe більшої ємності мають більше смуг (×2, ×4, ×8, ×16); на Raspberry Pi 5, BCM2712 підключено до нашого контролера введення/виведення RP1 через інтерфейс ×4.

Кожна лінія працює зі швидкістю 5 Гбіт/с для PCIe 2.0 (найшвидший режим, який ми офіційно підтримуємо на Raspberry Pi 5); після накладних витрат на кодування це перетворюється на пропускну здатність 4 Гбіт/с. Навіть враховуючи накладні витрати на інші протоколи, Ви, ймовірно, побачите ~450 Мбайт/с з хорошого NVMe SSD. Дійсно швидко!

Окрім каналів даних і годинника, специфікація PCIe вимагає деяких сигналів бічної смуги, таких як скидання, запит синхронізації (який виконує подвійну функцію як сигнал стану живлення) і пробудження.

Наш 16-контактний роз’єм забезпечує всі ці сигнали. У нас також є два штифти, які дозволяють нам контролювати живлення плати та гарантувати, що належним чином розроблений PIP (наше нове слово для PCIe Peripheral) автоматично розпізнається мікропрограмою Raspberry Pi.

Не М.2

Чому ми не додали роз’єм M.2 до Raspberry Pi 5? Роз’єм M.2 великий, відносно дорогий і вимагає від нас джерела живлення 3,3 В, 3 А. Разом це не дозволяє нам мати його в стандартному форм-факторі Raspberry Pi.

Використання невеликого недорогого роз’єму FFC дозволило нам забезпечити інтерфейс PCIe без збільшення плати або нав’язування вартості роз’єму M.2 і схеми його підтримки для кожного користувача Raspberry Pi.

Перше уточнення

Одна річ, яку ми не підготували до запуску Raspberry Pi 5, — це конкретика того, як створити периферійні пристрої, які підключаються до 16-контактного роз’єму PCIe. Взаємодія периферійних пристроїв PCIe зі станами живлення та мікропрограмою Raspberry Pi вимагала детального розгляду, і ми хотіли переконатися, що ми провели широке тестування нашого власного прототипу продукту, щоб переконатися, що все працює належним чином.

Сьогодні ми випускаємо першу редакцію цієї специфікації. Наш власний M.2 M Key HAT+ знаходиться на завершальній стадії прототипування та буде запущений на початку наступного року.

Друге уточнення

Для тих, хто уважно читає, ви помітили, що ми називаємо наш M.2 HAT «HAT +». Якщо вам не вистачило однієї нової специфікації, сьогодні ми також випускаємо попередню версію нової специфікації HAT +.

Оригінальна специфікація HAT була написана ще в 2014 році, тому прийшов час її оновити. Відтоді багато чого змінилося. Нова специфікація спрощує певні речі, зокрема необхідний вміст EEPROM, і об’єднує все в один документ у новому стилі документації Raspberry Pi, а також додає кілька нових функцій.

Над цим стандартом ще потрібно попрацювати, і наші утиліти EEPROM ще не оновлено для підтримки створення нового стилю EEPROM. Тож сьогоднішній випуск дуже підходить людям, які хочуть відчути і побачити, як змінюється стандарт HAT.

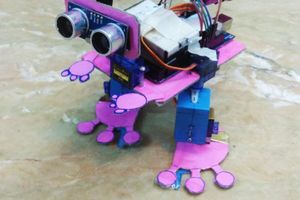

Ми справді хотіли створити правильний стандарт HAT+, оскільки він, імовірно, існуватиме так само довго, як і старий стандарт HAT. Однією з причин затримки публікації стандарту роз’єму PCIe було наше розуміння того, що плати PCIe (PIP!), які йдуть зверху, а не плати, які йдуть внизу, мабуть, повинні бути платами HAT+. Так і буде!

Різдвяні стандарти!

Ми сподіваємось, що два нових стандарти стануть приємним різдвяним матеріалом для читання. Якщо ви хочете обговорити їх із спільнотою, перейдіть на форуми Raspberry Pi, де ви знайдете спеціальну область для обговорення HAT, HAT+ та інших периферійних пристроїв.

Дивіться на цій сторінці новий M.2 HAT+ і остаточну версію стандарту HAT+, яку ми випустимо разом із ним у новому році.